在进行图像处理算法中,往往需要生成图像像素矩阵,这对于C语言来说可以直接用数组表示,但是对于verilog来说便不是那么容易了,硬件描述语言不比软件,它的核心不再算法,而是在于设计思想,加速硬件。在进行图像的滤波算法时,需要生成3x3矩阵,而altera的IP shift_ram 简直就是为矩阵运算而生的。下面便进行shift_ram的学习。

手册还是尽量看英文原版的比较好,刚开始是会比较痛苦,看习惯了就会发现,就是那么一些熟悉的单词,句子也很好理解,比较手册又不是文章。

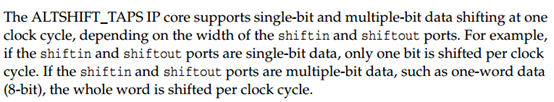

这段话的意思是,这个IP支持一个时钟周期移位一个或多个bit的数据,位宽是可以设置的。

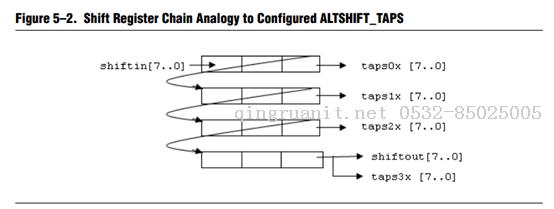

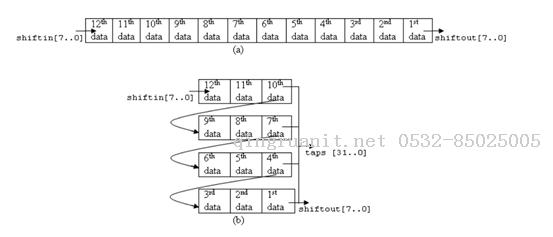

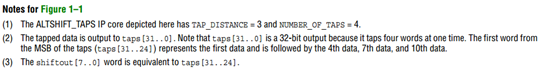

下面这个图是shift_ram的移位示意图,开始我一直以为是这个IP每存储三个数据就会进行移位到下一行,如果这样想当一行图像数据传过来的时候,显然如果是均值滤波的话,这是将第一行的数据进行了取中值操作,这样显然是不符合滤波的原理的。那么从这个图上所表达的貌似就是这个意思,为什么会出现这种矛盾。这也是一直困惑我的地方,还是手册没有好好看,手册上说的很清楚,图下一幅图所示。

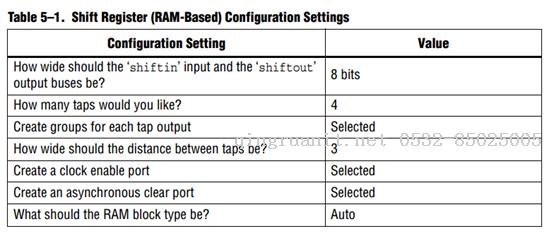

看Note所表明的,这里设置的行数是4行,每行的distance是3,所以便出现了这样的移位寄存,所以手册还是要仔细阅读的,我刚开始就是因为闲手册太麻烦便草草了事,后来实践证明,还是等弄清楚原理在下手操作,磨刀不误砍柴工。

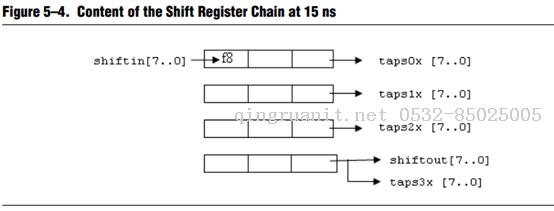

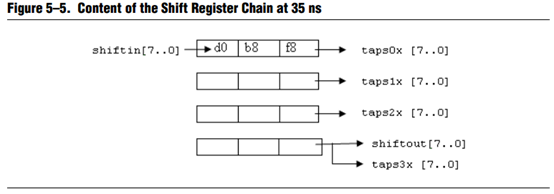

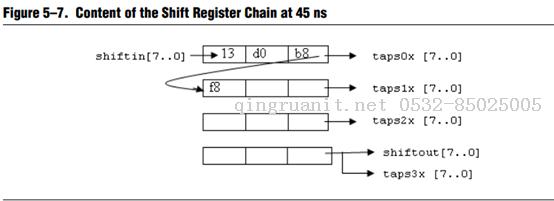

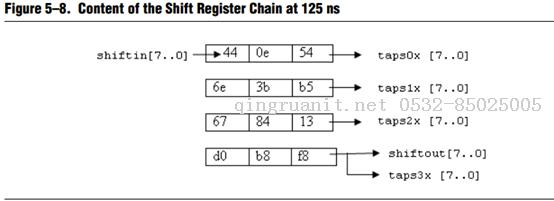

当然手册中也给了仿真例程

数据输入输出宽度为8bit,设置4行,选择每行宽度为3,添加使能和复位