前面讲解了使用EDA工具(主要是power compiler)进行功耗分析的流程,这里我们将介绍在数字IC中进行低功耗设计的方法,同时也结合EDA工具(主要是Design Compiler)如何实现。我们的讲解的低功耗设计主要是自顶向下的设计,也就是说,我们首先介绍在系统架构层面上如何进行低功耗设计(或者可以从哪些方面进行低功耗设计);然后我们在RTL层面和门级层面上介绍低功耗设计的方法,这两个种方法主要是依靠RTL代码和Design Compiler实现的,这是我们前端设计人员进行低功耗设计与优化所需要知道的,我们会着重介绍;最后我们简单介绍在物理设计层次上面降低功耗的方法。今天我们记录系统与架构级的低功耗设计。

1.系统与架构级低功耗设计

系统与架构层次的低功耗设计,可以节省70%以上的功耗。这个层次上的设计往往是由系统和架构设计人员进行的,这些人员往往是有着丰富经验的设计人员。他们制定了低功耗设计方案,由下一级的设计人员(比如做前端设计、做Flow的人员)进行具体实现。下面就来介绍一下在系统架构方面,可以从哪些方面进行低功耗设计,由于我只是只菜鸟,因此这些内容只是我在前人的经验中进行总结学习的笔记,仅供参考。

(1)多电压设计技术(Multi-VDD)

①多电压设计技术介绍

从前面的功耗方程中,我们可以知道,电压与功耗有着密切的联系。因此功耗的降低可以考虑使用低一点的电压。多电压设计技术有三种方式:

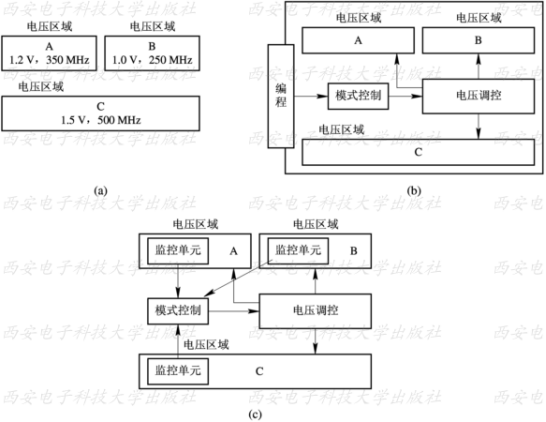

A:各电压区域有固定的电压,如上图(a)所示 ;

B:各电压区域具有固定的多个电压,由软件决定选择哪一个电压,如上图(b)所示;

C:自适应的方式,各电压域具有可变的,由软件决定选择哪一个电压,如上图(c)所示。

A是固定分配的电压;而B和C为动态电压管理,涉及到软硬件协同设计,这里我们放到后面进行介绍。这里主要是从整体上进行介绍多电压设计技术及其要求,然后给出A方式的一个例子以及一个多电压低功耗设计的脚本示例。

延伸阅读

学习是年轻人改变自己的最好方式

学习是年轻人改变自己的最好方式