本文如果有错,欢迎留言更正;此外,转载请标明出处 http://www.cnblogs.com/IClearner/ ,作者:IC_learner

前面介绍的设计都不算很复杂,都是使用时钟的默认行为作为电路的约束,都存在有路径给你约束,即信号的变化要在一个时钟周期内完成,并达到稳定值,以满足寄存器的建立和保持的要求。此外进行可测性设计(design for test)时,为了提高测试的覆盖率,我们经常使用多路(multiplex,简称mux)传输电路的控制时钟,使电路的时钟信号可以由输入端直接控制。这些电路约束属于复杂的约束,除了理论上的讲解之外,还会进行实战,实战内容主要为围绕前面的伪路径和多周期路径进行的,主要内容如下:

·异步设计路径和逻辑上不存在的路径的时序约束(时序例外)

·多时钟周期的时序约束

·分频电路和多路时钟传输的时钟约束

·实战

1、异步设计路径和逻辑上不存在的路径的时序约束(时序例外)

(1)异步设计的路径约束

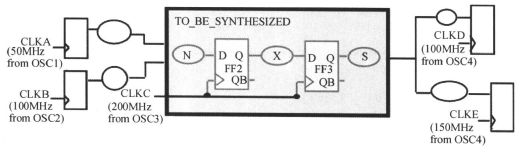

前面说的都是同步时序电路,下面就用介绍一下异步时序电路的约束吧。异步时序电路的时钟来自不同的时钟,模块之间的时钟是不同频或者同频不同相的关系,一些时钟在我们的设计里没有对应的端口,如下图所示:

上图中,一共用4个时钟源,有5种不同的时钟;我们要综合电路使用的是时钟CLKC,时钟源是OSC3,前后模块的时钟各不一样,因此是异步电路。

(在传统的同步和