三、门级电路低功耗设计优化

(1)门级电路的功耗优化综述

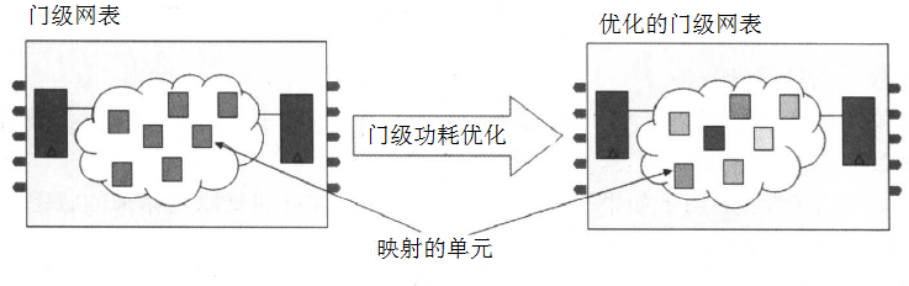

门级电路的功耗优化(Gate Level Power Optimization,简称GLPO)是从已经映射的门级网表开始,对设计进行功耗的优化以满足功耗的约束,同时设计保持其性能,即满足设计规则和时序的要求。功耗优化前的设计是已经映射到工艺库的电路,如下图所示:

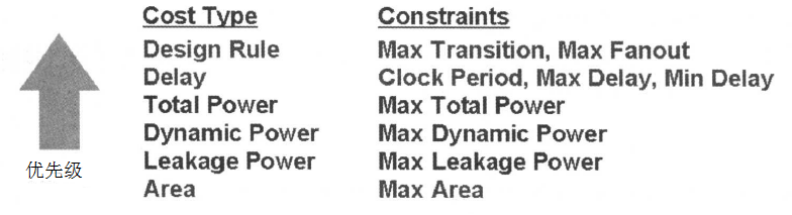

门级电路的功耗优化包括了设计总功耗,动态功耗以及漏电功耗的优化。对设计做优化时,优化的优先次序如下:

由此我们可以找到, 优化时,所产生的电路首先要满足设计规则的要求,然后满足延迟(时序)约束的要求,在满足时序性能要求的基础上,进行总功耗的优化,再进行动态功耗的优化和漏电功耗的优化,最后对面积进行优化。

优化时先满足更高级优先权的约束。进行低级优先权约束的优化不能以牺牲更高优先权的约束为代价。功耗的优化不能降低设计的时序。为了有效地进行功耗优化,需要设计中有正的时间冗余(timing slacks)。功耗的减少以时序路径的正时间冗余作为交换,即功耗优化时会减少时序路径上的正的时间冗余。因此,设计中正的时间冗余越多,就越有潜力降低功耗。

通过上面的描述,对门级功耗优化有了一下了解之后,这里先介绍一下静态功耗优化的方法——多阈值电压设计,然后介绍基于EDA工具的动态功耗的优化,接着介绍总体功耗的优化;在最后介绍一种常用的门级低功耗的方法——电源门控。电源门控我放在明天发表,今天的内容主要就是围绕静态、动态、总功耗来写。

网友评论